ניהול זכרון

ארגון זיכרון ה-RAM הפנימי של המעבד:

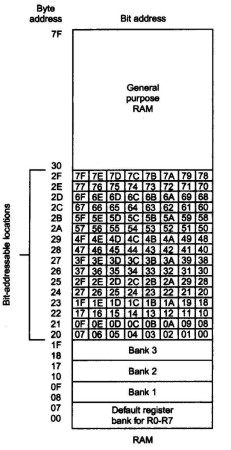

ה-RAM הפנימי הוא בן 256 בתים המחולקים לשני חלקים. חלק אחד נקרא INTERNAL DATA RAM (RAM נתונים פנימי) והוא כולל את הבתים מ- 00h עד 7Fh . החלק השני נקרא SPECIAL FUNCTION REGISTERS (אוגרי פונקציות מיוחדות).

אזור RAM הנתונים הפנימי מורכב מששה חלקים בצורה הבאה:

האזורים 1 עד 4 מכילים כל אחד 8 בתים. הם מאפשרים להשתמש בבתים שונים כאוגרים R0-R7 . ל - 8751 סידרת הוראות המטפלת באוגרים R0-R7 . הבחירה באיזה בנק ממוענים R0-R7 נעשית בעזרת אוגר המצב הכלול באוגרים המיוחדים. הבחירה בין האזורים נעשית ע"י קביעת תוכן סיביות RS0 ו-RS1 ,שבאוגר המצב (PSW ).

0,0 ב-RS1,RS0 ממען את האוגרים ל-BANK 0 (בתים 00H-07H)

0,1 ב-RS1,RS0 ממען את האוגרים ל-BANK 1 (בתים 08H-0FH)

1,0 ב-RS1,RS0 ממען את האוגרים ל-BANK 2 (בתים 10H-17H)

1,1 ב-RS1,RS0 ממען את האוגרים ל-BANK 3 (בתים 18H-1FH)

אזור 5 הוא RAM שניתן לטיפול בסיביותיו בשתי צורות. צורה אחת ע"י פניה במעון ישיר לבתים 20H עד 2FH. אפשרות אחרת היא בעזרת פקודות במעון סיבית. בפקודה מעין זו פונים לכל סיבית ישירות. לכל סיבית יש כתובת בת 8 סיביות משלה, כמתואר בציור הקודם.

אזור 6 הוא אזור RAM ישיר רגיל בן 80 בתים בתחום 30H עד 7FH .

החלק השני של ה-RAM (SPECIAL FUNCTION REGISTERS), בתיו מהווים למעשה אוגרים מיוחדים. האוגרים מתוארים ברשימה לפי הפונקציות שלהם:

| שם האוגר | כתובת | כינוי | שם מלא | הערה |

| הצובר | E0H | ACC | ACCUMULATOR | * |

| אוגר B | F0H | B | B REGISTER | * |

| אוגר מצב | D0H | PSW | PROGRAM STATUS WORD | * |

| מצביע מחסנית | 81H | SP | STACK POINTER | |

| הבית הגבוה של DPTR 0 | 83H | DP0H | DATA POINTER 0 HIGH BYTE | |

| הבית הנמוך של DPTR 0 | 82H | DP0L | DATA POINTER 0 LOW BYTE | |

| הבית הגבוה

של DPTR 1 |

85H | DP1H | DATA POINTER 1 HIGH BYTE | |

| הבית הנמוך של DPTR 1 | 84H | DP1L | DATA POINTER 1 LOW BYTE | |

| פורט 0 | 80H | P0 | PORT 0 | * |

| פורט 1 | 90H | P1 | PORT 1 | * |

| פורט 2 | A0H | P2 | PORT 2 | * |

| פורט 3 | B0H | P3 | PORT 3 | * |

| בקרת עדיפות פסיקות | B8H | IP | INTERRUPT PRIORITY CONTROL | * |

| בקרת אפשור פסיקות | A8H | IE | INTERRUPT ENABLE CONTROL | * |

| בקרת אופן מונה/קוצב זמן | 89H | TMOD | TIMER/COUNTER MODE CONTROL | |

| בקרת אופן מונה/קוצב זמן | C8H | T2MOD | TIMER/COUNTER 2 MODE CONTROL | |

| בקרת מונה / קוצב זמן | 88H | TCON | TIMER/COUNTER CONTROL | |

| הבית הגבוה של TIMER0 | 8CH | TH0 | TIMER/COUNTER 0 BYTE HIGH | |

| הבית הנמוך של TIMER0 | 8AH | TL0 | TIMER/COUNTER 0 BYTE LOW | |

| הבית הגבוה של TIMER1 | 8DH | TH1 | TIMER/COUNTER 1 BYTE HIGH | |

| הבית הנמוך של TIMER1 | 8BH | TL1 | TIMER/COUNTER 1 BYTE LOW | |

| הבית הגבוה של TIMER2 | CDH | TH2 | TIMER/COUNTER 2 BYTE HIGH | |

| הבית הנמוך של TIMER2 | CCH | TL2 | TIMER/COUNTER 2 BYTE LOW | |

| אוגר טעינה או תפיסה הגבוה | CBH | RCAP2H | CAPTURE\RELODE REGISTER HIGH | |

| אוגר טעינה או תפיסה הנמוך | CAH | RCAP2L | CAPTURE\RELODE REGISTER LOW | |

| אוגר בקרת הזיכרון ו- W.D.T | 96H | WMCON | WATCHDOG AND MEMORY CONTROL REGISTER | |

| אוגר המידע של יחידת הממשק | 86H | SPDR | SPI DATA REGISTER | |

| אוגר המצב של יחידת הממשק | AAH | SPSR | SPI STATUS REGISTER | |

| אוגר בקרת יחידת הממשק | D5H | SPCR | SPI CONTROL REGISTER | |

| בקרת שידור וקליטה טוריים | 98H | SCON | SERIAL CONTROL | * |

| חוצץ נתונים טורי | 99H | SBUF | SERIAL DATA BUFFER | |

| בקרת ספק | 87H | PCON | POWER CONTROL |

הערה : כל האוגרים המסומנים ב- * , ניתן לפנות לסיביותיהם במיעון סיבית בהתאם לאיור הבא:

פניה לזכרון חיצוני:

הפניה לזכרון חיצוני נעשת ע"י ריבוב רגלי 0P בזמן כלומר תחילה מסופקים על פורט זה הBIT8 התחתונים של הכתובת הרצויה לאחר מכן מופיע אות ברגל ALE שמשמש האות בקרה לנעילת הכתובת בLATCH לאחר נעילת הכתובת משמש פורט זה להעברת DATA.

- כדי להורות למיקרו-בקר שיש לפנות לזיכרון חיצוני ברגל 'EA צריך להופיע "0".

- רגל 'PSEN מאפשרת את רכיב הזיכרון.

תהליך קריאה או כתיבה לזכרון חיצוני נמשך מחזור מכונה אחד - 3 STATS עבור הOPCODE ועד 3 STATS עבור האופרנדים.